Computers and Technology, 08.12.2020 16:40 oprajapati

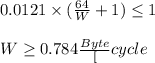

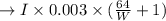

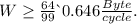

A. Suppose a CPU with a write-through, write-allocate cache achieves a CPI of 2. What are the read and write bandwidths (measured by bytes per cycle) between RAM and the cache?

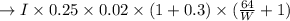

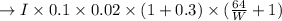

b. For a write-back, write allocate cache, assuming 30% of replaced data cache blocks are dirty, what are the read and write bandwidths needed for a CPI of 2?

Data Reads per 1000 instructions Data Writes per 1000 instructions Instruction Cahce Miss Rate Data Cache Miss Rate Block size (Bytes)

250 100 0.30% 2% 64

Answers: 2

Another question on Computers and Technology

Computers and Technology, 21.06.2019 17:20

The thickness of a part is to have an upper specification of 0.925 and a lower specification of 0.870 mm. the average of the process is currently 0.917 with a standard deviation of 0.005. determine the percentage of product above 0.93 mm.

Answers: 3

Computers and Technology, 23.06.2019 05:00

Jason works as an accountant in a department store. he needs to keep a daily record of all the invoices issued by the store. which file naming convention would him the most?

Answers: 2

Computers and Technology, 23.06.2019 08:00

What is a scenario where records stored in a computer frequently need to be checked

Answers: 2

Computers and Technology, 23.06.2019 20:10

Leo is a recruitment executive for a large company. he has identified new labor resource requirements in both the marketing and production departments. what should be his first step in recruiting candidates for the positions? a. conduct background checks of candidates b. make job offers c. arrange interviews d. conduct reference checks e. place job ads on job sites

Answers: 1

You know the right answer?

A. Suppose a CPU with a write-through, write-allocate cache achieves a CPI of 2. What are the read a...

Questions

Mathematics, 20.02.2021 09:20

Mathematics, 20.02.2021 09:20

Mathematics, 20.02.2021 09:20

Mathematics, 20.02.2021 09:20

English, 20.02.2021 09:20

English, 20.02.2021 09:20

Mathematics, 20.02.2021 09:20

Computers and Technology, 20.02.2021 09:20

Mathematics, 20.02.2021 09:20

Health, 20.02.2021 09:20

Social Studies, 20.02.2021 09:20

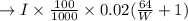

, Hit time + miss penalty Hit time:

, Hit time + miss penalty Hit time:![= I + I \times [0.25 \times 0.02 + 0.1 \times 0.02 + 0.003] \times (\frac{64}{W} + 1) \leq I \times 2.](/tpl/images/0960/7133/03573.png)

![= I + I \times [0.25 \times 0.02 \times 1.3 + 0.1 \times 0.02\times 1.3 + 0.003]\times (\frac{64}{W} + 1) \leq 2I](/tpl/images/0960/7133/32a7d.png)